第20章 SPI 协议

串行外设接口SPI (Serial Peripheral Interface) 总线由摩托罗拉开发,用于实现主设备与从设备之间的全双工同步串行通信。SPI总线通常用于与闪存、传感器、实时时钟(RTC)、模数转换器等设备进行通信。

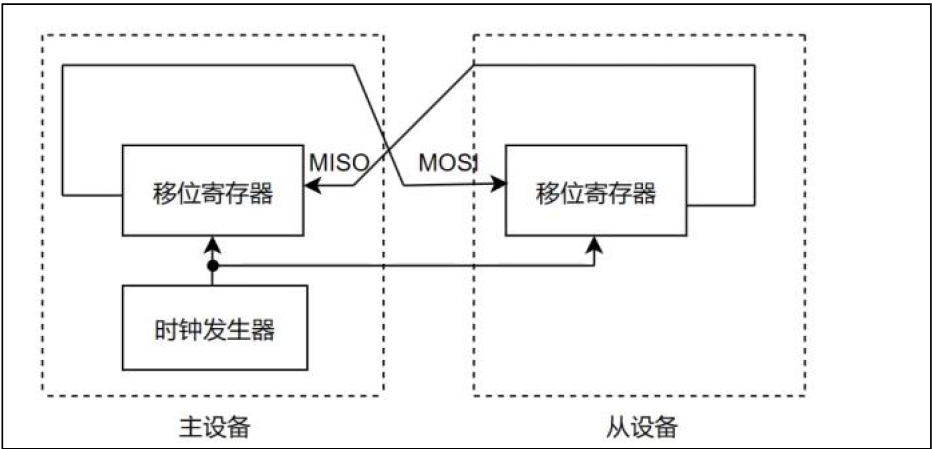

如下图所示,标准SPI主设备通过串行时钟(SCK)、主输出从输入(MOSI)、主输入从输出(MISO)和从设备选择(SS)线与从设备进行通信。SCK、MOSI和MISO信号可以被多个从设备共享,而每个从设备都有一个唯一的SS线。

20.1 SPI 硬件连接

SPI 使用4 根信号线进行通信,分别是SCLK、MOSI、MISO 和 CS, 如下:

SCLK (Serial Clock):时钟信号线

由主设备产生的同步时钟信号,用于驱动数据的收发。主设备负责提供稳定的时钟信号,频率可以根据需要进行调整。从设备需要使用这个时钟信号来对齐和采样数据。

MOSI (Master Output Slave Input):主->从数据传输线

主设备向从设备传输数据的线路。主设备将要发送的数据放在这条线上,从设备则从这条线上读取数据。

MISO (Master Input Slave Output):从->主数据传输线

从设备向主设备传输数据的线路。从设备将要发送的数据放在这条线上,主设备则从这条线上读取数据。

CS (Chip Select) 或SS (Slave Select):片选/从设备选择信号

主设备用来选择与之通信的从设备的信号线。当主设备拉低某个从设备的CS/SS 线时, 表示选中了该从设备进行通信。主设备可以通过控制多个CS/SS 线来选择与不同从设备通信。

20.2 SPI 通信原理

SPI 总线在进行数据传输时,具有以下特点:

传输顺序:默认情况下,SPI 总线先传输高位(MSB,Most Significant Bit),然后传输低位(LSB,Least Significant Bit)。

逻辑电平:数据线为高电平表示逻辑1,数据线为低电平表示逻辑0。

字节传输:一个字节传输完成之后,无需应答信号即可开启下一个字节的传输。

SPI 是单通信协议,意味着总线中只有一个主设备能发起通信,而SPI 主设备和从设备都有一个串行移位寄存器,如下图所示:

当SPI 主设备想读/写从设备时,它首先要拉低从设备对应的CS 线(CS 线是低电平有效),接着开始发送工作脉冲到时钟线上,在相应的脉冲时间上,主设备把信号发送到MOSI 实现 “写”,同时可对MISO 采样实现“读”,然后通过一个实际的例子对上述内容进行讲解,假设要将主设备的数据0x00 发送给从设备,从设备现在的移位寄存器值为0xff, 传输的具体示意

图表如下所示:

根据表格可以得到数据传输实际上就是主设备和从设备之间进行的数据交换,在一个SPI时钟周期内,收发是同时进行的,主机通过MOSI 线发送1bit 数据,从机通过该线读取这1bit数据;从机通过MISO 线发送1bit 数据,主机通过该线读取这1bit 数据;当寄存器中的内容全部移出时,相当于完成了俩个寄存器内容的交换。

如果主设备要给从设备传输数据,主设备只需要忽略掉从设备接收到的数据即可。如果主设备要从从设备接收数据,主设备向从设备随机发送数据,从设备忽略掉从主设备接收的数据即可。

20.3 SPI 极性和相位

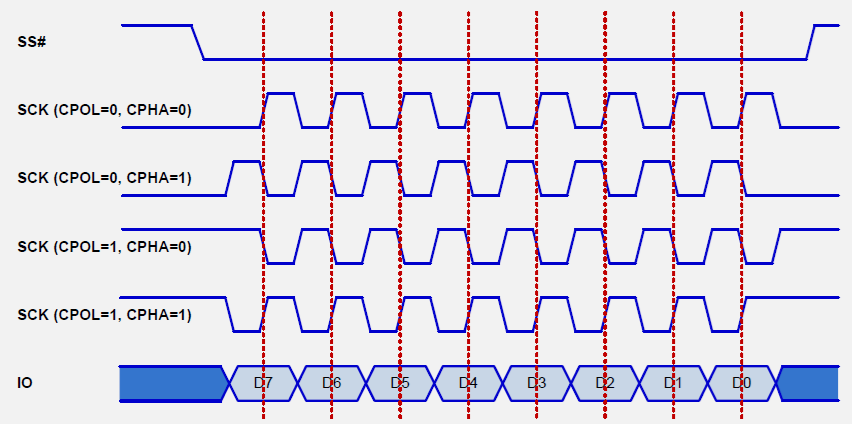

SPI总线并没有定义数据交换的协议,从而减少了开销,允许高速数据传输。时钟极性(CPOL)和时钟相位(CPHA)可以设定为‘0’或‘1’,形成四种独特的模式,以提供主设备与从设备之间的灵活通信,如下图所示。

CPOL(时钟极性Clock Polarity)

CPOL 定义了时钟信号的默认状态(即空闲状态)。

CPOL = 0 时,表示时钟信号在空闲状态下为低电平(0)。

CPOL = 1 时,表示时钟信号在空闲状态下为高电平(1)。

CPHA(时钟相位Clock Phase)

CPHA 定义了数据信号相对于时钟信号的采样时间。

CPHA = 0 时,表示数据在时钟的第一个边沿(上升或下降)被采样。

CPHA = 1 时,表示数据在时钟的第二个边沿(上升或下降)被采样。

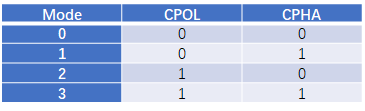

SPI 有如下4种工作模式:

模式0(CPOL = 0,CPHA = 0):在时钟的上升沿采样数据,这种模式是SPI从设备通信中最常见的。

模式1(CPOL = 0,CPHA = 1):在时钟的下降沿采样数据。

模式2(CPOL = 1,CPHA = 0):在时钟的下降沿采样数据。

模式3(CPOL = 1,CPHA = 1):在时钟的上升沿采样数据。

即SPI工作模式, 如下表:

因此,主设备和从设备必须配置相同的CPOL 和CPHA,否则无法正常通信。而在一般情况下,主设备会配置CPOL 和CPHA,从设备则需要根据主设备的设置进行匹配。